【DDR系列】從基礎理論、布局布線以及后期的測試及調試【轉發】

2018-04-10 by:CAE仿真在線 來源:互聯網

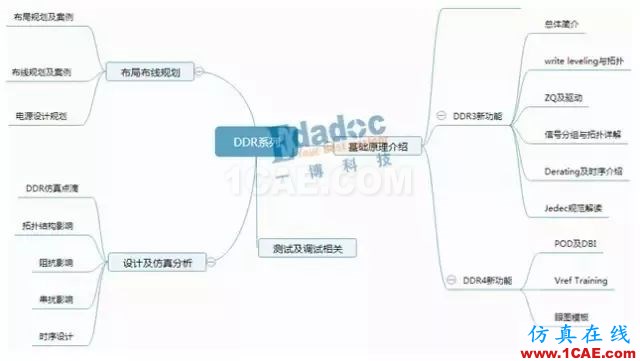

DDR相關的文章一直是備受大家喜歡,大概跟大家的工作相關度較高吧。接下來的合輯就是DDR系列了,通過合輯可以讓大家系統的學習DDR相關的基礎知識和設計及仿真技巧。

01

DDR系列之開篇

本系列共分四大部分,分別是基礎理論介紹,布局布線規劃介紹,設計及仿真分析以及后期的測試及調試上的一些案例介紹。這個是目前的一個規劃,其中基礎理論的一些介紹網上的資料也一大把,所以我們只是簡單的一些介紹,期間會根據大家的意見和反饋再添加一些機動內容,側重點還是在具體的工程實踐上,如怎么設計和仿真,遇到問題了怎么去解決,夠接地氣了吧!

02

DDR的前世與今生(一)

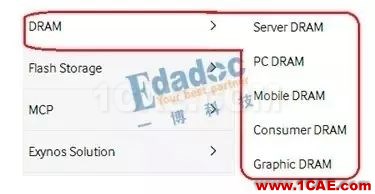

DDR SDRAM全稱為Double Data Rate SDRAM,中文名為“雙倍數據率SDRAM”。DDR是在原有的SDRAM的基礎上改進而來,嚴格的說DDR應該叫DDR SDRAM,人們習慣稱為DDR。說到這里,很多人可能會問SDRAM、DRAM、SRAM或者RAM、ROM到底是什么鬼,怎么區別的?小編還是來簡單普及下關于存儲的基礎知識吧。

03

DDR的前世與今生(二)

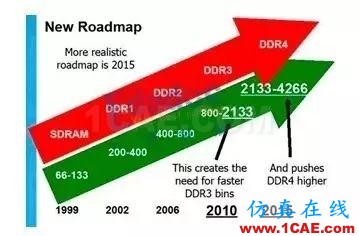

SDRAM是比較久遠的事情了,但我們一說到它肯定不會和DDR混淆,我們通常理解的SDRAM其實是SDR SDRAM,為SDRAM的第一代,而DDR1則為第二代,乃至到我們現在使用的DDR4,其實為第五代SDRAM,在此需要澄清一下。以示區別,后續文章里面用SDR來特指SDR SDRAM,而DDR就特指DDR SDRAM了。

04

DDRx的關鍵技術介紹(上)

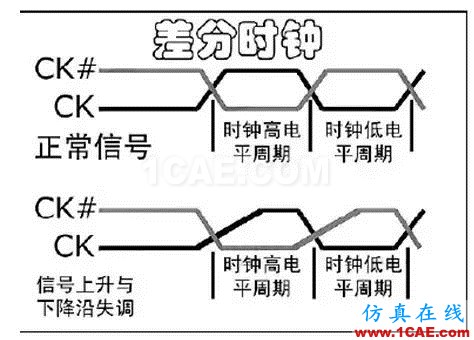

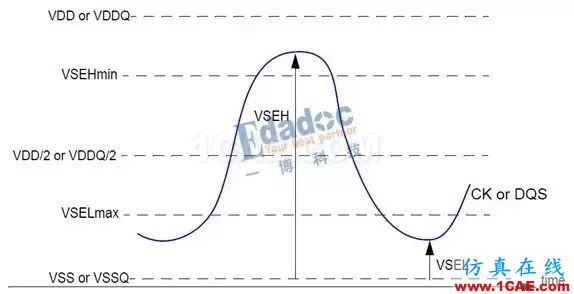

差分時鐘是DDR的一個重要且必要的設計,但大家對CK#(CKN)的作用認識很少,很多人理解為第二個觸發時鐘,其實它的真實作用是起到觸發時鐘校準的作用。由于數據是在CK的上下沿觸發,造成傳輸周期縮短了一半,因此必須要保證傳輸周期的穩定以確保數據的正確傳輸,這就要求CK的上下沿間距要有精確的控制。

05

DDRx的關鍵技術介紹(下)

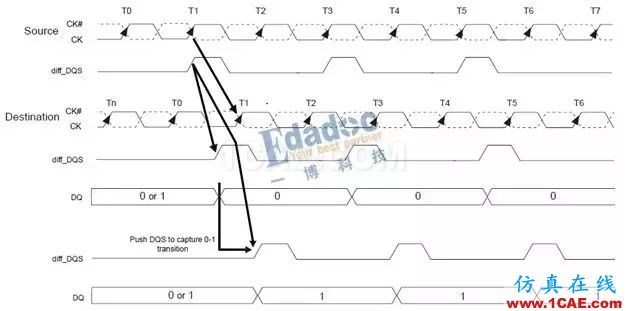

Write leveling功能和Fly_by拓撲密不可分。Fly_by拓撲主要應用于時鐘、地址、命令和控制信號,該拓撲可以有效的減少stub的數量和他們的長度,但是卻會導致時鐘和Strobe信號在每個芯片上的飛行時間偏移,這使得控制器(FPGA或者CPU)很難保持tDQSS、tDSS 和tDSH這些參數滿足時序規格。

06

走進JEDEC,解讀DDR(上)

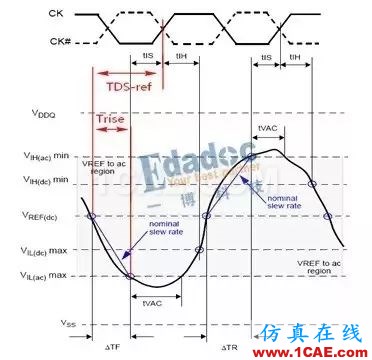

通常,DDR設計完成之后 ,對信號質量并沒有一個完全確定的概念,需要我們通過仿真和測試的手段去判斷和驗證。而此時,往往我們拿到的就是一個波形,測試波形或者仿真波形,該如何去判斷其信號質量,參照的標準又是怎樣的,就是我們需要去考慮的重點。

07

走進JEDEC,解讀DDR(下)

首先,我們計算建立時間的margin的時候,都是由UI/2-建立時間,實際上此時的建立時間是tIS(total setup time)= tIS(base)+derating, derating是對建立保持時間基準值的修正。對于tIS的定義,為什么會需要用到derating這個參數呢,這實際和規范中tIS(base)的定義方式相關。

轉自公眾號:一博科技高速先生

相關標簽搜索:【DDR系列】從基礎理論、布局布線以及后期的測試及調試【轉發】 HFSS電磁分析培訓 HFSS培訓課程 HFSS技術教程 HFSS無線電仿真 HFSS電磁場仿真 HFSS學習 HFSS視頻教程 天線基礎知識 HFSS代做 天線代做 Fluent、CFX流體分析 HFSS電磁分析