高速AD/DAC的測量及設計問題解答

2016-12-25 by:CAE仿真在線 來源:互聯網

高速ADC和DAC是現代無線通訊系統或雷達系統的關鍵器件之一。下面分別介

紹高速ADC和高速DAC的測試指標、測試系統搭建和指標計算方法。

1、ADC的主要參數

ADC的主要指標分為靜態指標和動態指標2大類。

靜態指標主要有:

? Differential Non-Linearity (DNL)

? Integral Non-Linearity (INL)

? Offset Error

? Full Scale Gain Error

動態指標主要有:

? Total harmonic distortion (THD)

? Signal-to-noise plus distortion (SINAD)

? Effective Number of Bits (ENOB)

? Signal-to-noise ratio (SNR)

? Spurious free dynamic range (SFDR)

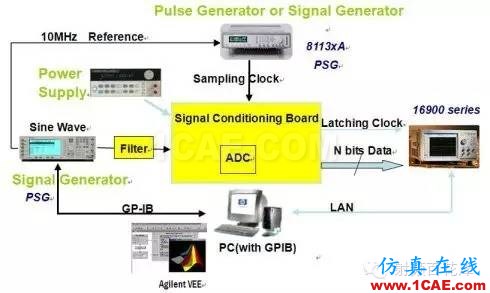

2、ADC的測試方案

要進行ADC這些眾多指標的驗證,基本的方法是給ADC的輸入端輸入一個理想的信號,然后對ADC轉換以后的數據進行采集和分析,因此,ADC的性能測試需要多臺儀器的配合并用軟件對測試結果進行分析。下圖是一個典型的ADC測試方案:

圖1 典型的高速ADC測試系統方案

3、ADC測試結果的分析

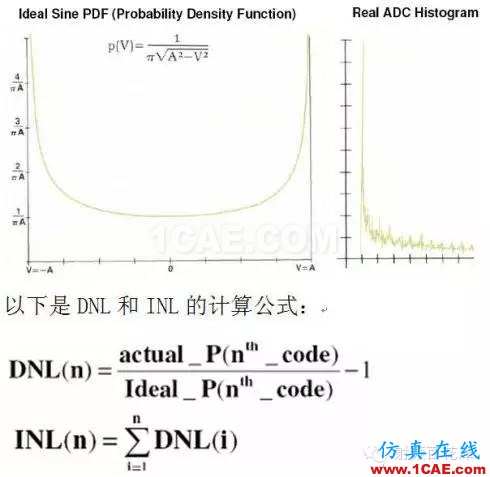

ADC的靜態指標是對正弦波的采樣數據進行幅度分布的直方圖統計間接計算得到,如下圖所示,理想正想波的幅度分布應該是左面的形狀,由于非線性等的影響,分布可能會變成右邊的形狀,通過對直方圖分析可以得出靜態參數的指標。

圖2 ADC靜態指標分析方法

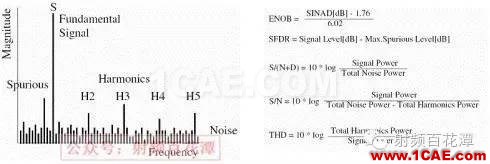

ADC的動態指標是對正弦波的采樣數據進行FFT頻譜分析間接計算得到。一個理想的正弦波經A/D采樣再做頻譜分析可能會變成如下圖的形狀,除了主要的正弦波分量以外還產生了很多噪聲、諧波和雜散,通過對這些分量的運算,可以得到ADC的動態參數。

圖3 ADC動態指標的計算公式

4、DAC的主要參數

DAC的作用是和ADC相反,是把數字量轉換成模擬量,雖然有模擬和數字的區別,但是DAC要測試的主要指標與ADC類似,也分為靜態指標和動態指標2大類。

靜態指標主要有:

? Differential Non-Linearity (DNL)

? Integral Non-Linearity (INL)

? Offset Error

? Full Scale Gain Error

? Conversion Rate

? Settling Time

? Rising/Falling Time

動態指標主要有:

? Total harmonic distortion (THD)

? Signal-to-noise plus distortion (SINAD)

? Effective Number of Bits (ENOB)

? Signal-to-noise ratio (SNR)

? Spurious free dynamic range (SFDR)

5、DAC的測試方案

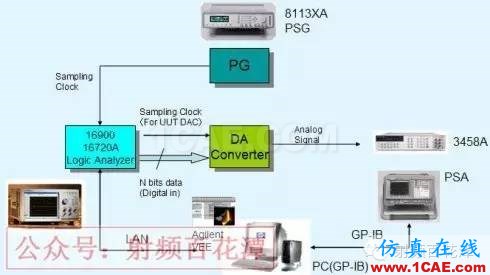

對于DAC來說,測試方法正好和ADC相反,是在輸入端加數字激勵信號,在模擬輸出端測試其輸出性能的指標。下圖是一個DAC的測試方案:

圖4 典型的高速DAC測試系統方案

6、DAC測試結果的分析

對于DAC來說,測試不同參數碼型發生器發出的數據是不同的,所用的分析儀器也不同。

1、用碼型發生器發出數值順序從0至(2^n-1)的階梯波,每增加一個數值,用萬用表測量一下相應DAC輸出端的電壓。測量出每個數字輸入值對應的真實模擬輸出量后就可以得出INL、DNL、Gain Error、Offset Error等信息。

2、用碼型發生器產生數值從0至(2^n-1)來回跳變的三角波,逐漸增加碼型發出速度,直至模擬輸出低于剛才的滿量程范圍1LSB。通過這種方法可以判斷DAC的Conversion Rate。

3、用碼型發生器產生數值從0至(2^n-1)的階躍脈沖,用示波器測量輸出波形的Settling Time、Rising/Falling Time等參數。

4、對于動態參數的測試,是預先在碼型發生器里放入一組正弦波的數字波形,然后送給DAC轉換成真正的模擬正弦波信號,用頻譜儀對波形的諧波失真、雜散、噪聲等做分析。計算公式同ADC。

1.如何選擇高速模數轉換之前的信號調理器件;如何解決多路模數轉換的同步問題?

ADC之前的信號調理,最根本的原則就是信號調理引起的噪聲和誤差要在ADC的1個LSB之內。根據這個目的,可以需要選擇指標合適的運放。至于多路ADC同步的問題,一般在高速ADC的數據手冊中都會有一章來介紹多片同步問題,你可以看一下里面的介紹。

2.在挑選ADC時如何確定內部噪聲這個參數?

一般ADC都有信噪比SNR或者信納比SINAD這個參數,SINAD=6.02*有效位數+1.76,您可以根據這個公式來確定您選擇的ADC能否符合您的要求.

3.如何對流水線結構ADC進行校準?需要校準哪些參數?

一般來講,ADC的offset和gain error會比較容易校準。只要外接0V和full scale進行采樣,然后得到校準系數。另外,如果需要作溫度補償的話,一般需要加一個溫度傳感器,然后利用查表的方式來補償。

4.對ADC和DAC周圍的布線有哪些建議?

ADC和DAC屬于模擬數字混合型器件,在布局布線時最重要的是要注意地分割,即模擬地和數字地的處理問題。對于高采樣率的器件,建議使用一塊地。而低采樣率的器件,建議模擬數字地分開,最后在芯片下方連接在一起。

其他的布局布線規范與其他器件的是一樣的。

對于具體的器件,一般會有評估板的Layout圖可供參考。

5.模數轉換器的精度與噪聲系數之間有什么必然的聯系嗎?

低速模數轉換器的精度用峰峰值分辨率,有效值分辨率來表示。在ADI一些Sigma-delta ADC的芯片資料里都會列出不同情況下的有效值分辨率指標。高速模數轉換器的精度可用SNR,SNOB來表示,這些指標也可在資料中找到。

但一般ADC的指標中不會有噪聲系數(NF)的指標。

6.如果采用了外部模擬切換開關,那么這個開關總是存在一些電阻的,必然引起一些誤差,那么我想問一下有沒有什么辦法能減少這些誤差,分別描述一下用硬件的方法與用軟件的方法。

你可以選擇電阻很小的開關比如ADG14**系列。如果是開關是做通道切換的,在后級加一個運放跟隨就可以了。如果是做量程切換,只能選擇電阻很小的開關,同時注意開關的平坦度和溫度漂移參數,如果系統精度要求很高,那就只能做軟件校正或者選擇可編程放大器如AD8250/1/3等。

7.將AD7710的輸入端與自身的地短接后,再讀取數據時,其AD轉換值跳動比較大,通過說明當中的幾種校準方式,都沒有解決?頻率已經在25Hz上了。不知如何解決?

請確認電源和基準的穩定性,在頻率為25Hz,增益為1的條件下,看數據手測上Table II可知其有效值分辨率為21.5bit,那么其實際的峰峰值分辨率為21.5-2.7=18.8bit,也就是說如果有5bit碼在跳就是正常的。

8.請問ADC的輸入和傳感器相連,如何將傳感器輸出信號本身的干擾排除?

如果傳感器輸出是共模干擾,需要加儀表運放如AD8221/0等濾除。如果是差模干擾,加濾波器就可以濾除。

9.我要設計一個16路的數據采集系統,每路的采樣率為100K,16BIT,請問一下,我要采用什么樣的AD芯片,另外,AD轉換器的輸入通道比較少,要選擇什么樣的外部多路模擬切換開關?另,對模擬切換開關的選擇有什么要求,要關注哪些參數。

我們沒有16bit和16通道的ADC,您可以選擇用兩片AD7689,16bit 8通道。或者選擇16:1的ADG1206.要注意導通電阻,注入電荷,導通時間等。

10.一個12位的高速模數轉換器能不能降低以及如何降低到8位來使用,因我們的系統精度只需要8位,高了反而有害。

你在讀取數據的時候,只需要讀8bit即可。

11.有一些ADC集成有抗混疊濾波器,請問有什么好處?

一般抗混疊濾波器指的是ADC前端的濾波器,而sigma-delta ADC內部會集成一些陷波器,來實現工頻50Hz和60Hz陷波,總的好處就是ADC有更好的抗噪聲性能。

12.請問怎樣才能降低相鄰通道相互間的干擾?

在布局布線時可以考慮在相鄰通道間加地屏蔽。

13.想設計高精度校準儀表,如直流電壓輸出(毫伏級),能不能推薦幾款芯片?請問怎樣消除伴隨的量化噪聲?如何保證ADC的精度,AD轉換的滿量程即是電源電壓,對于單電源供電,零點的確定和量程都與電源電壓有關,如果電源電壓波動勢必導致轉換的誤差,電路中如何解決,特別對小信號的采集.請問什么是DAC的輸出靜態誤差?怎樣提高數模轉換器中電阻或者電流源單元的匹配程度?在給ADC供電時,數字地與模擬地之間是否需要串接小電感?

1)ADI的運放,儀放產品種類很多,最好把詳細的指標要求列出來,這樣比較容易找。

2)ADC的量化噪聲是固有的,沒辦法消除。

3)ADC的電源對測量精度有直接的影響。所以要選擇高精度低噪聲的電源信號,且在布線的時候也要注意避免干擾。

4)一般手冊里會分別給出zero error,gain error等等,不知道具體問的是哪一個,或者可以舉一個具體型號的例子。

5)這應該是DAC內部結構的問題,一般來講,我們不關心內部電阻或電流源的絕對值,只關心它們之間的比例,現在的工藝可以很好地保證這個。

6)一般來講,用0歐姆電阻連接就可以了。

14.ADC的內部增益越大,其產生的噪聲也越大,專家能說說兩者之間的原理是什么?

ADC內部的PGA增益越大,本身PGA的噪聲會增加,另外ADC輸入噪聲被放大的越多。所以ADC內部增益越大,分辨率越小。

15.電源紋波對轉換精度的影響 ?

如果ADC有PSRR這個指標,可以使用這個指標去算電源紋波對ADC的影響。如果沒有,一般基準源都有這個指標,你可以使用基準源的PSRR去算對ADC采樣的影響。

16.數據轉換器在布線長度、通信串擾和匹配電阻等方面是如何設計的?

高速ADC會考慮這些問題。尤其對于LVDS接口的ADC,盡量保證一對信號的布線等長等距,放置端接電阻。這方面的布局布線最好是參考評估板來做。

17.ADI產品高速數模轉換最大速度能達到多少?采樣頻率大了是不是穩定性會下降?

我們的DAC的最大速度能達到2.5GHZ,它是AD9739電流輸出型的,這不會影響到穩定性。

18.ADC的標稱的位數很高,但是實際中末尾的幾位會被內部噪聲而淹沒,我在挑選ADC時如何確定內部噪聲這個參數?

對于高精度的ADC,一般來講都會給出一個有效分辨率的參數,也就是器件可以達到不跳碼的位數。另外在設計中還有考慮電源,參考電壓的噪聲,以及ADC前端調理電路引入的噪聲。需要把這些噪聲控制在ADC的1個LSB之內。

19.評估ADC的時候,因為評估SNR,比較困難,所以我一般會考慮評估在接地時候的跳碼程度來比較兩種同類ADC的差異,這種評估方法科學嗎?有沒有更科學的方法?有沒有具體的文檔?

實際上對于高速ADC來說,應該是加一個高精度的基準信號,而后用ADC采樣,再做FFT分析來評估SNR。而對于高精度的ADC來說才是您用的辦法,可以參考我們的應用筆記AN-835。

20.如何理解壓擺率這個指標?為什么要對電壓變化率做限制?

舉個簡單的例子,如果壓擺率不夠,那么就是實際的輸出跟不上輸入信號的變化,這樣對信號的處理就會有失真。

21.開關電源的紋波對12位以上的ADC的影響有多大?是否需要為ADC部分單獨處理電源紋波?

高精度的ADC,比如16位及以上的ADC,不建議使用開關電源來供電。

22.請問使用高功效開關穩壓器替換傳統的LDO穩壓器電源對高速模數轉換器有沒有負面影響?對產品壽命有何影響?

在高速ADC場合,一般對電源的紋波和噪聲有較高的要求。開關電源效率比較高,但是有較大的紋波和噪聲,會對系統的精度有影響。而高速場合對SNR,SFDR要求比較高,所以選擇LDO會比較好。

23.關于運算放大器的阻抗匹配在設計中,需要如何注意?

只有在高速的情況下才需要考慮阻抗匹配,我們在網站上有一個軟件可以直接幫助您計算阻抗匹配的,請看如下鏈接:http://www.analog.com/en/tools-software-simulation-models/resources/amplifiers-and-comparators/differential-amplifiers/index.html

24.電源精度會導致ADC的精度提不上去嗎?

有可能。具體要看你ADC的位數和PSRR這個參數。如果位數很低如10bit,你用再低噪聲的電源也只能是10bit精度。但是16bit系統,你如果使用噪聲很大的電源,會使得系統精度不能達到16bit。

25.AD前抗射頻干擾濾波器一般應當達到什么樣的性能指標呢,比如截至頻率,滾降 ?

這取決于您的實際應用,當然理想情況下是截至頻率等于有效的輸入信號,而滾降特性是無限陡峭,但實際上沒有這樣的濾波器,且越接近理想情況,成本會越高,要折衷考慮。

26.如何抑制輸入"毛刺"?

加濾波器抑制,或者是對采樣結果做數字濾波。

27.有什么好的建議,使用軟件來提高ADC的精度與位數?

請注意參考和電源的質量,同時還需要注意layout來防止噪聲引入。

28.請問對于ECG信號的AD轉換需要有多大的分辨率?可以推薦幾款型號嗎?

取決于ECG的信號鏈。如果信號鏈中為AC隔離,這樣信號可以被放大很大,比如放大1000倍,這樣ADC的選取12位~16位。如果信號鏈為DC隔離,這樣信號不能被放大很多,一般增益為10,這樣ADC的位數就得選的大些,18位~24位。

ECG產品會有相應的標準,即ECG產品最小能分辨多小的信號,ADC的選取與此也有關。

29.我設計的一個基于FPGA的DDS系統中使用的芯片是AD9777,請問在電流足夠的情況下,系統電源設計中是否可以將DA芯片與FPGA芯片共用3.3V數字電源,以達到簡化電源設計的目的?

可以 。

30.隨著數字視頻信號應用的越來越普及,數模轉換器在視頻方面會不會無用武之地,乃至被淘汰

數模轉換器是不會被淘汰的,因為最終都是要將數字信號轉會人們能所識別的模擬信號。

31.惡劣環境下(高溫下),ADC的供電電源怎么設計?一般DC-DC很難達到+85攝氏度,ADI是否有相關的參考設計?

選擇合適的器件,DC-DC能工作在85度,關鍵是你選擇合適的器件和合適的設計,使得系統的溫升在其標定的范圍,如加風扇或者散熱片,多個器件并聯提高電源效率等。

32.我在使用ADuC841的A/D時,采集的數據偶爾會時零,為什么?如何解決?

這種情況要用示波器監測輸入信號,看輸入端是否真的發生跳變了,如果沒有請仔細檢查ADUC841的數據讀取程序。

33.請問把一個直流信號加到轉換器輸入端時,怎樣確定輸出端應該出現的數碼數目?

一般來講,根據計算公式,Vin/Vref=code/2^N. N為ADC的位數,Vin為輸入電壓,Vref為參考電壓。如果是有負電壓,需要考慮輸出碼字的類型,比如二進制補碼等等。絕大多數ADC的數據手冊中都會給出一個圖來說明這個問題。

34.AD7710使用時,噪音過高。如何使用說明書當中的校準?在布線過程當中如何做比較合適?

建議參考芯片的評估板來做Layout設計。

35.請問怎樣盡量減小系統噪音對ADC的影響?

盡量減少輸入噪音(可以差分輸入的ADC),減小電源噪音。設計合適的濾波器等。

36.如何確定溫度對基準的影響以及多最終轉換精度的影響

基準芯片資料中會有相關溫度對基準影響的溫度系數指標,一般為幾個ppm/°C。

一般ADC芯片資料沒有參考電壓隨溫度變化對ADC性能影響的測試參數。

37.如何實現對高速ADC的THD測試?

實際中是加一個高精度的基準源,而后用ADC采樣,再做FFT分析,具體請見AN-835上面的介紹。

38.有什么辦法可以減少開關電源的噪聲對ADC的影響?

加入LC濾波,合理的layout如模擬地數字地分開。如果還不行,只能加低噪聲的LDO。

39.如果ADC的傳遞函數線形度比較差,如何進行校準,有沒有通過驗證比較科學的方法?是否可以舉例說明?

一般情況下都是做線性校正的,如果校正后還不能滿足要求,那建議采用分段校正的方法。

40.相對于單端,差分有很多優勢,但是還是有很多單端的ADC,差分模式有什么弱點嗎?

和單端的輸入相比,外圍的電路相對復雜一些。

41.請問在高速數據采集系統設計中,我們怎樣來確定采樣率和存儲器帶寬?

采樣率由待處理信號的頻率決定。存儲器帶寬由采樣率和處理器能力來決定。

42.請問AD前抗射頻干擾濾波器一般應當達到什么樣的性能指標 ?

這取決于您的應用,理想情況下就是只讓有效帶寬內的信號通過,但濾波器設計很難達到理想情況,所以要折衷考慮。

43.如果對視頻信號進行數模/模數轉換該如何選擇轉換器,它的關鍵性規格是哪幾個方面呢 ?

主要是要看您所需要轉換的視頻信號格式,需不需要做色彩空間轉換。是普通的并口接口還是HDMI的接口。

44.ADC的輸出延時主要受什么因素的影響?

這是由ADC的內部參數決定的,具體要看不同型號的數據手冊。

45.請問如何減小截斷誤差和增益誤差?

對一個特定的ADC來說,它的Offset誤差和Gain誤差基本是一定的。但是Offset誤差和Gain誤差是可以通過軟件校正消除的。

46.采集的數據中總是有錯誤的代碼,有何種方法能夠消除此錯誤代碼?

要先確定錯誤代碼是ADC輸出錯誤還是MCU讀取錯誤。如果是前者,那得看系統的設計是否合理,布局布線是否合理。

47.開關電源的地是否需要和ADC的模擬地分開嗎 ?

ADC的模擬地通過一點接入開關電源輸出濾波電容的地會減小電源紋波對ADC的影響。

48.PSRR指標指什么?

指的是電源電壓抑制比。

49.最近我鑒定一只雙電源ADC。 我將待測轉換器的輸入端接地, 并 且在LED 指示燈上觀察其輸出的數碼。 令我非常驚奇的是為什么我所觀察到的輸出數碼范圍不是我所期望的一個數碼?

導致這個問題的原因有很多種:輸入信號源的范圍,參考電壓源的值,噪音的影響等等。

50.ADC的量化噪聲為什么沒辦法消除?

因為采樣不是理想,而是無限逼近的概念。

51.實際應用中INL、DNL那個指標對用戶更有意義?

這兩個指標都比較重要。

52.模擬地與數字地最后的連接方式應該是怎么樣的?

盡量將模擬地和數字地分開,為了避免相互的干擾。但是在高速的ADC應用中,數字和模擬要求共地。

53.我現在需要安裝節省空間的數據轉換器,認為串行式轉換器比較適合。為了選擇和使用這種轉換器,請問我需要了解些什么?

串行接口的ADC一般轉換速度比較低,在10M以下,但是封裝,讀取會比較方便。你可以先看看你需要的位數,以低于10M的速度能不能滿足你的要求。另外關鍵是MCU和ADC的接口,是使用模擬的SPI還是MCU的標準SPI接口。

54.對ad的時鐘信號有什么要求?需不需要做一些溫度、抖動方面的補償?

不需要做補償。ADC中內部已經做了相關的補償。

55.對于單板結構,板子上有多個比如9片ADC的話,本講座是建議ADC跨接模擬地和數字地?是否意味著要多點接地?

ADC需要接在系統的模擬部分。

56.什么時候用FPBW,什么時候用小信號BW,數據手冊并沒有把所有情況告訴我們。

FPBW與芯片的Slew Rate有關,當要把信號放大時,如果Slew Rate跟不上,輸出信號就會失真。FPBW = SlewRate/2piVp,Vp為輸出信號的電壓。

57.請教專家,在采用R、C隔離時,若R較大會影響后面的ADC,若C較大會影響相位,具體設計時應該如何選擇呢?

可以考慮在RC濾波后加一級運放做buffer.

58.數據轉換器中最常見的錯誤主要有哪些?如何避免

ADC轉換會受到Noise的影響,如果ADC轉換的結果與理論值大概相等,那么可以通過在同一個輸入電壓上讀多次轉換結果,將轉換結果平均來得到更為準確的值。

59.我們要的帶寬為100hz,結果用的是帶寬為1khz的放大器,如何有效解決抗干擾問題?

一般來講,ADC前端需要加一個濾波,濾掉把有用帶寬以外的噪聲。

60.影響ADC的重要參數有哪些?如何在pcb設計中避免?

考慮ADC前端的抗混疊濾波器的設計,阻抗匹配,輸入輸出的阻抗。

61.在高速模數轉換時,是不是不能以芯片內部的參考電壓為準,都需要外部參考,有沒有可能芯片內部參考電壓也達到一般外部參考那么穩定?

使用內部參考電壓,由于參考電壓在ADC轉換時會sink/source電流,這會影響ADC的電源電壓,進而影響ADC的SNR。一般系統精度要求很高的場合常使用外部參考。

62.目前ADI公司的ADC芯片中,分辨率高于14bit,最高速率能達到多少?雙通道,分辨率高于14bit,最高速率能達到多少?

14bit的ADC最高為150MSPS。可以到一下網址來搜索。http://www.analog.com/dynamic/parametric/scResultsDisplay.asp?SearchType=PSS&ProductLine=ADC&la=en

63.傳遞函數不連續(DNL不連續)會導致什么問題?如果應用中遇到這個問題,我應該如何處理?使用軟件補償嗎?如果不連續,為什么芯片不能從硬件角度去做補償?

DNL不連續會導致丟碼,這個問題沒有辦法在外部做補償,這是ADC本身的特性。ADI的ADC都是保證沒有丟碼的問題存在的。

64.開關電源對數據轉換出錯的影響有多大?開關電源的頻率建議多高最為合理?

你可以加LDO或者LC濾波器減小電源紋波和噪聲。一般ADC的PSRR會比較高,位數低的ADC如10bit對電源要求不高,但高位數的ADC如16bit對開關電源要求比較高。開關電源頻率選擇和功率,效率有關。普通的開關頻率一般選擇為100KHz-300KHz。

65.從信噪比角度來看,要實現多路AD,是采用單個多路AD的芯片實現?還是用多個個單路的AD實現好?

采用多個ADC芯片效果會更好。因為單芯片多通道的芯片,通道之間會有干擾。

66.怎樣判斷轉換錯誤是干擾信號引起的還是轉換本身引起的?

對于高頻的要用高精度的基準源,高精度的可以將輸入端短路來測試ADC本身上的噪聲特性。

67.為了降低高頻干擾,開關穩壓器后面使用LDO是否有好處?

會有好處。你可以選擇低噪聲的LDO。

68.那種類型的A/D在進行布線的時候,要特別的注意電磁干擾的抑制?有什么好的建議?

一般來講ADC不需要考慮這個,而是在電源端考慮電磁干擾抑制。如果用到高速的數字器件或者時鐘的話,可以考慮加一個屏蔽罩。

69.陷波器和抗混疊濾波器有什么不同?

陷波器就是將某一頻率下的干擾做足夠的衰減,可以理解為帶阻濾波器,而抗混疊濾波器可以理解為低通濾波器。

70.噪聲混疊是否會導致ADC的SNR下降?

混疊是由于采樣率<2倍的信號頻率是產生的,這是會使得濾波器的設計變得困難,從而噪聲的濾除變得困難,SNR也會受到影響。

71.由LDO向ADC供電改為使用開關電源向ADC供電時,對EMC性能的影響?

這要看你開關電源的EMC處理情況,如果開關電源EMC/I處理不好,系統就有EMI/C問題。由LDO向ADC供電改為使用開關電源向ADC供電可能會影響ADC的精度。

72.如果測量的是很低頻率的模擬信號(小于10Hz),直接單端測量和將信號轉換成差分信號后驅動ADC相比,哪種方式測量精度會更高?

你可以直接單端測量就可以。

73.脈沖模式的A/D時序控制復雜嗎?是A/D內部實現的嗎?

對于用戶端來說,都是用CPU控制ADC的通信接口,這并不復雜。

74.為了消除噪聲干擾,如何才能盡量減少AC環路 ?

布局布線的時候要盡量考慮信號線的回流路徑,使得回路面積盡量小。

75.現在想做一個項目用到16位的高速ADC,但是前端模擬信號本身的噪聲比較大,會浪費掉3~4位的精度,為此你們覺得選擇16位的ADC有必要嗎?

如果輸入信號本身的噪聲只要12位,而且無法通過處理來降低噪聲,那么就不要使用16bit的ADC。

76.一般ADC封裝上都有很多模擬電源引腳,比如AD7656就有8個AVcc,在設計PCB時,如何把他們連接到電源上?

最好是有一層電源平面,就近將AVCC接到電源上,注意電容的分布。新設計建議使用AD7656-1,與AD7656相比,-1電源引腳上需要的電容較少。

77.專家是否能推薦幾款低溫漂的Rail-to-Rail的高精度運算放大器呢?

AD8628、AD8638

78.現在的系統中很多都是單一的開關電源供電,那么對于系統中ADC、DAC的數字電源、模擬電源、數字地、模擬地,要如何處理?

數字電源可以通過一個磁珠后從模擬電源引出。如果允許,盡量使用分離的電源芯片為模擬和數字電源供電。

79.有些ADC會在時鐘輸入端加入高頻抖動源,這樣做能夠提升adc的有效位數么?

可以用單電源供電,但要注意AD620的Reference需要接到0.5的電源電壓處。

80.請問采樣時如何才能避免信號的丟失?

只能通過提高采樣率或濾波。

81.如何區分干擾是從前端進去的?還是從電源進去的?

對于高精度的應用,可以把輸入端短路來測輸出,如果干擾依然不變,就應該是電源和參考等引起的。

82.高速ADC和低速ADC在干擾的處理上有什么不同嗎?

相同的是加入去藕電容來消除干擾。layout可能有些不同,高速ADC一般采樣地平面,就近接地,低速一般是數字地模擬地分開,單地接地。

相關標簽搜索:高速AD/DAC的測量及設計問題解答 HFSS電磁分析培訓 HFSS培訓課程 HFSS技術教程 HFSS無線電仿真 HFSS電磁場仿真 HFSS學習 HFSS視頻教程 天線基礎知識 HFSS代做 天線代做 Fluent、CFX流體分析 HFSS電磁分析