電源完整性如何進行測試驗證?/成品PCB的外形公差,層間位移公差各是多少?

2016-11-07 by:CAE仿真在線 來源:互聯網

轉:微信群"SI-list 中國【1】"聊天記錄:

————— 2015-12-10 —————

若華 上午7:57

請問下電源完整性如何進行測試驗證

李黎明 上午7:59

@蔣方 ?好問題!

荊棘鳥 上午7:59

量壓降?

荊棘鳥 上午8:00

負載電壓波動?

若華 上午8:01

很多東西仿真可以做。但是覺得為什么要這么做 效果如何呢? 好像PI不像Si那么好測試驗證吧?請教各位有經驗的大師

李黎明 上午8:03

平面層阻抗很低,測試同軸一般50,這可是業界難題.

楊雪冬 上午8:05

@李黎明(Shark4685)?直接用示波器不行嗎?

楊安毅 上午8:05

請教一個問題,仿出來目標阻抗怎么用測試驗證?

楊安毅 上午8:06

如果測試無法驗證,仿真結果怎么衡量準確性

李黎明 上午8:07

需要寬頻s參數

李黎明 上午8:09

還有它是動態的

若華 上午8:10

@李黎明(Shark4685)?平面層阻抗怎么測

若華 上午8:11

目標阻抗只是假想的一個理想指吧 ?

李黎明 上午8:13

keysight有個專門儀器

李黎明 上午8:13

zte國內這個有些發言權

若華 上午8:14

儀器名字是什么 我 查查看 謝謝

李黎明 上午8:16

等我啃完這個餅

若華 上午8:16

[呲牙][呲牙] 多謝多謝李總

qzheng 上午8:18

5062

若華 上午8:19

除了這些電源完整性還利用什么儀器測試驗證哪些參數嗎?

若華 上午8:19

謝謝

周振東 上午8:21

tek的DSA8300也可以測

周振東 上午8:23

還需要測串擾吧

干柴 上午8:25

這個群真好,一大早就技術大研討,專家們邊啃餅邊交流[呲牙]

李黎明 上午8:26

周振東 上午8:27

[強]

曲國遠 上午8:27

測平面和測信號的網分不一樣嗎?

李黎明 上午8:27

不一樣

楊安毅 上午8:28

8300應該測不了吧,精度達不到

偉~笑向暖@ 上午8:30

pi測試驗證是比較難的吧?@李黎明(Shark4685)

李黎明 上午8:33

@遲大偉?我個人感覺,要對pi有一定的理解,認知才好動手.測只是最后一環

李黎明 上午8:34

群2的牛人,用示波器點下電源,看下頻譜就定位問題了![衰]

楊安毅 上午8:37

最終還是需要測試!

若華 上午8:39

舉個例子 對某個芯片的去耦電容仿真優化如何測試和驗證這樣做的效果

瘋子 上午8:41

@李黎明(Shark4685) 怎么做到的

荊棘鳥 上午8:44

@李黎明(Shark4685)?負載和頻譜什么關系?

李黎明 上午8:45

人家對自己設計單位東西很了解.

李黎明 上午9:03

我們有個客戶,電容都邊測試邊焊接的!

瘋子 上午9:05

什么產品啊,要求這么高

黃躍輝 上午9:05

電容邊測試邊焊接[強]敬業!

于爭 上午9:06

PDN阻抗,用失網,雙端口測如果板上只有電容,仿測擬合非常好

瘋子 上午9:09

有什么好用的云操作系統沒

李黎明 上午9:42

@楊雪冬-西安電子工程研究所?楊主任,外形尺寸一般公差+-5mil,要求高的+-2mil,@于爭?層間位移同一張core+-2mil,不同的core,8層以上+-8mil.

紅塵天使 上午9:42

對于ddr2.-4片和一片ecc星形結構,有好的處理方式嗎?

紅塵天使 上午9:42

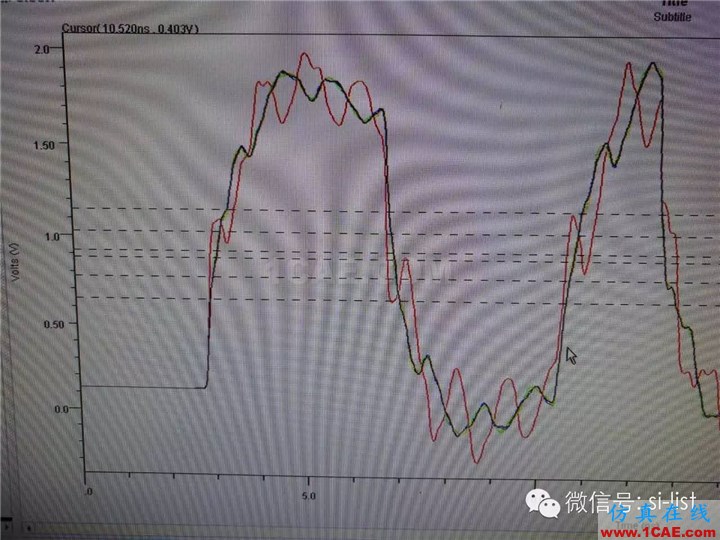

仿真結果

紅塵天使 上午9:42

對于ddr2.-4片和一片ecc星形結構,有好的處理方式嗎?

紅塵天使 上午9:42

仿真結果

紅塵天使 上午9:43

紅塵天使 上午9:43

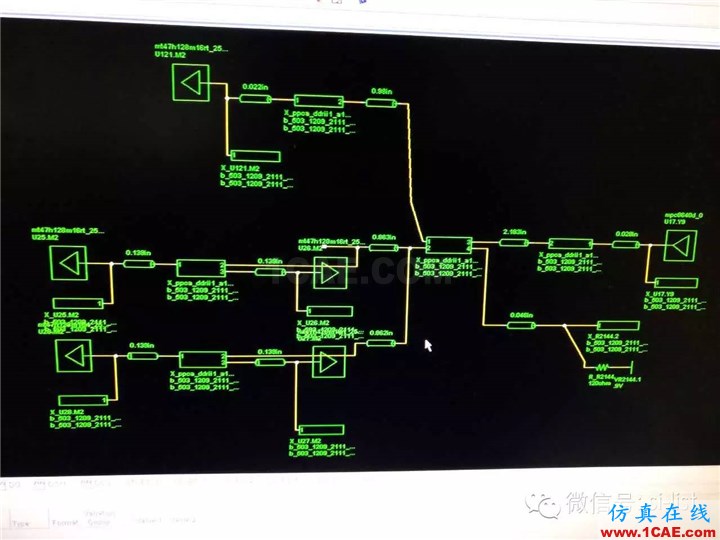

拓撲結構

紅塵天使 上午9:43

李黎明 上午9:51

sorry[壞笑]

李黎明 上午9:55

上面是極限值,一般會比這個好!

李黎明 上午9:56

@紅塵天使?ecc放通道第一顆,正反貼,數據走t拓撲結構

丹東 上午9:59

@瘋子?我有個朋友是做云系統的,有需要可以聯系。

楊雪冬 上午10:05

@李黎明(Shark4685)?公差幫我查了嗎?

汪進進_鼎陽科技 上午10:07

[FFT之于頻譜分析儀 : http://mp.weixin.qq.com/s?__biz=MjM5Nzc1NzM0NQ==&mid=401798147&idx=1&sn=06a8970a6d7e2b3ff287deab5e97fe74&scene=1&srcid=12102yOFYaosRv8QxbYq90Qh#rd]

李黎明 上午10:09

@楊雪冬-西安電子工程研究所?楊主任,外形尺寸一般公差+-5mil,要求高的+-2mil,@于爭?層間位移同一張core+-2mil,不同的core,8層以上+-8mil.

楊雪冬 上午10:11

@李黎明(Shark4685)?收到,多謝

紅塵天使 上午10:15

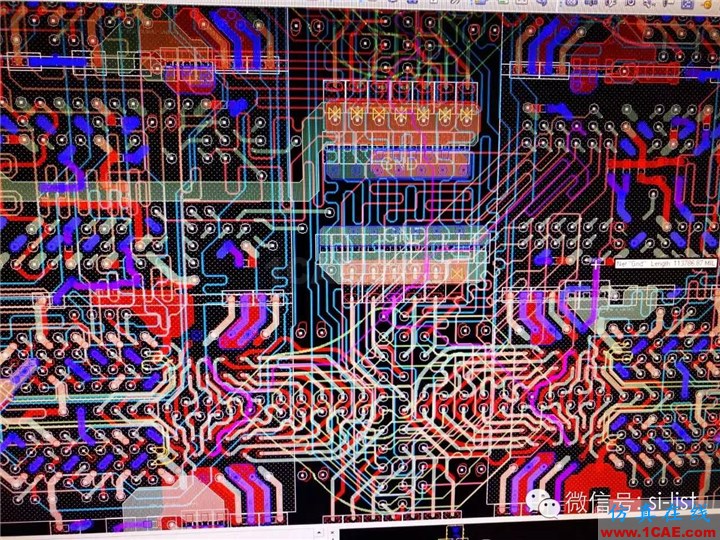

紅塵天使 上午10:15

是這樣放置的

瘋子 上午10:20

@丹東 謝謝

藍風 上午10:49

層間位移,8層以上+-8mil [驚訝]

朱江 上午10:58

大廠不至于

邵鵬 上午11:01

我估計@李黎明(Shark4685)?謙虛了,說的是最壞情況吧,但是5mil是很常見的。經特殊控制也要2mil。

藍風 上午11:01

是呀,嚇了我一跳,對位就8mil偏差,加上孔位孔徑偏差,就太大了

藍風 上午11:01

我也覺得@李黎明(Shark4685) 口誤了

藍風 上午11:02

5mil應該都是包含了孔位孔徑偏差在里面,要不然孔壁到線的距離就不夠了

李黎明 上午11:20

正常8層,3core,5-6mil左右,上面是極限值,一般會好!

相關標簽搜索:電源完整性如何進行測試驗證?/成品PCB的外形公差,層間位移公差各是多少? 電源完整性如何進行測試驗證 HFSS電磁分析培訓 HFSS培訓課程 HFSS技術教程 HFSS無線電仿真 HFSS電磁場仿真 HFSS學習 HFSS視頻教程 天線基礎知識 HFSS代做 天線代做 Fluent、CFX流體分析